# IMPINJ E910, E710, E510, AND E310 RAIN RFID READER CHIPS DATASHEET

Version 4

© 2024, Impinj Inc.

www.impinj.com

## **OVERVIEW**

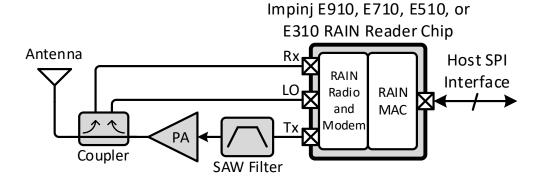

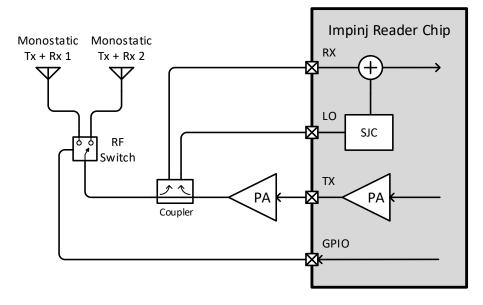

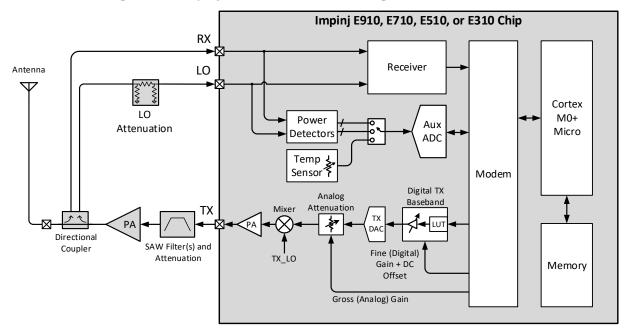

This document constitutes the electrical, mechanical, and thermal specifications for the Impinj<sup>®</sup> E910, E710, E510, and E310 RAIN RFID reader chips. It contains a functional overview, mechanical characteristics, package signal locations, and targeted electrical specifications. An overview of the capabilities of the reader chips are shown in Table 1, and a reader system block diagram is shown in Figure 1.

#### Table 1: Impinj E910, E710, E510, and E310 Reader Chips Overview

| Specification                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Air Interface Protocol              | <ul> <li>EPCglobal<sup>®</sup> UHF Class 1 Gen 2 / ISO 18000-63 RFID</li> <li>Supports Impinj Gen2X – an enhancement to the RAIN radio standard</li> <li>DSB-ASK, PR-ASK transmit modulation modes</li> <li>Dense reader mode (DRM) supported</li> </ul>                                                                                                                                                                                                                 |  |  |

| Chip Transmit<br>Output Power       | Configurable up to +11 dBm. (External power amplifiers supported for high performance applications, up to 33 dBm total Tx Power)                                                                                                                                                                                                                                                                                                                                         |  |  |

| Chip Receive<br>Sensitivity         | <ul> <li>Impinj E910: -103 dBm</li> <li>Impinj E710: -98 dBm</li> <li>Impinj E510: -93 dBm</li> <li>Impinj E510: -93 dBm</li> <li>Impinj E310: -84.5 dBm</li> <li>Note: All values in most sensitive Gen2 reader mode (20 µs TARI, 160 kHz BLF, Miller-8) at 10% PER in the "Ideal" antenna emulation configuration (described in Table 13) at the chip Rx pin Sensitivity is improved by 3-5 dB across all SKUs when operating Impinj Gen2X inventory rounds</li> </ul> |  |  |

| Tag Read Rates                      | <ul> <li>1000+ tags per second</li> <li>Note: Impinj E910 or E710, in FCC fastest RF mode, FW v1.1+. See Table 10 for details.</li> </ul>                                                                                                                                                                                                                                                                                                                                |  |  |

| Operating Frequencies 860 - 930 MHz |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Supported Regions                   | <ul> <li>All worldwide regions supported, including:</li> <li>US, Canada, and other regions following US FCC 47 CFR Ch. 1 Part 15</li> <li>Europe and other regions following ETSI EN 302 208-1 (v3.3.1)</li> <li>China, Japan, and other worldwide regions</li> </ul>                                                                                                                                                                                                   |  |  |

| Integration                         | RAIN Radio, Modem, MAC, RF Baluns, and Power Detectors included                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Power                               | Low power consumption: (configuration dependent) <ul> <li>Active: 550 to 1000 mW</li> <li>Idle: 28 to 55 mW</li> <li>Disabled: 0.1 to 0.5 mW</li> </ul>                                                                                                                                                                                                                                                                                                                  |  |  |

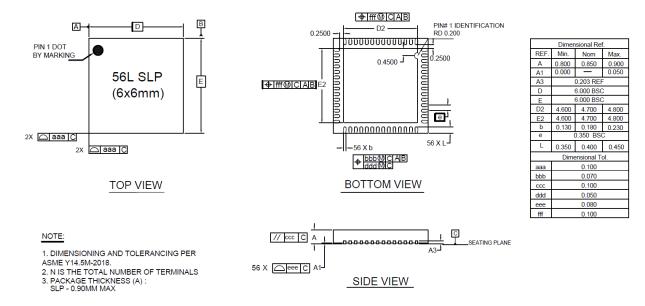

| Package                             | 56-pin 6 mm x 6 mm sawn QFN, 0.85 mm thickness, 0.35 mm pitch                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

#### Figure 1 – Impinj Reader Chip-Based Circuit Block Diagram

## **TABLE OF CONTENTS**

|                | Table of Figuresiii                  |    |  |  |

|----------------|--------------------------------------|----|--|--|

|                | Tables                               |    |  |  |

| 1 Intr         | oduction                             |    |  |  |

| 1.1            | Impinj E Family Features Summary     |    |  |  |

| 1.1.1          |                                      |    |  |  |

| 1.1.2          |                                      |    |  |  |

| 1.1.3          |                                      |    |  |  |

| 1.2            | Reference Documents                  |    |  |  |

| 1.3            | Block Diagram                        |    |  |  |

|                | cifications                          |    |  |  |

| 2.1            | Pin Listing and Signal Definitions   |    |  |  |

| 2.2            | IO Connections and Configurations    |    |  |  |

| 2.2.1          |                                      |    |  |  |

| 2.2.2          |                                      |    |  |  |

| 2.2.3          |                                      |    |  |  |

| 2.3            | Power Supply                         |    |  |  |

| 2.3.           |                                      |    |  |  |

| 2.3.2          |                                      |    |  |  |

| 2.3.3          |                                      |    |  |  |

| 2.4            | Electrical Specifications            |    |  |  |

| 2.4.1<br>2.4.2 |                                      |    |  |  |

| 2.4.2          |                                      |    |  |  |

| 2.4.           |                                      | 10 |  |  |

| 2.4.           |                                      |    |  |  |

| 2.4.0          |                                      |    |  |  |

| 2.4.0          |                                      |    |  |  |

| 2.4.8          |                                      | 20 |  |  |

| 2.4.0          |                                      |    |  |  |

|                | ictional Description                 |    |  |  |

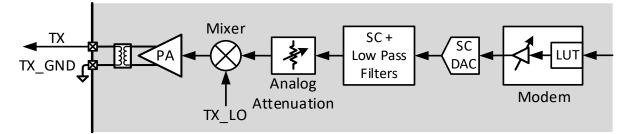

| 3.1            | Analog Transmitter Path              |    |  |  |

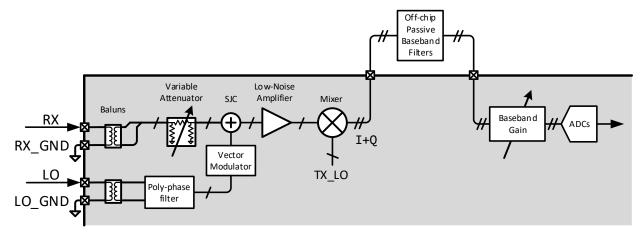

| 3.2            | Analog Receiver Data Path            |    |  |  |

| 3.2.1          |                                      |    |  |  |

| 3.2.2          |                                      |    |  |  |

| 3.2.3          |                                      |    |  |  |

| 3.2.4          |                                      |    |  |  |

| 3.3            | Antenna Configuration Scenarios      |    |  |  |

| 3.4            | RF TX, LO, and RX Path Configuration |    |  |  |

| 3.5            | RF Power Detection                   |    |  |  |

| 3.6            | Frequency Generation                 |    |  |  |

| 3.6.1          |                                      |    |  |  |

| 3.6.2          |                                      |    |  |  |

| 3.6.3          |                                      |    |  |  |

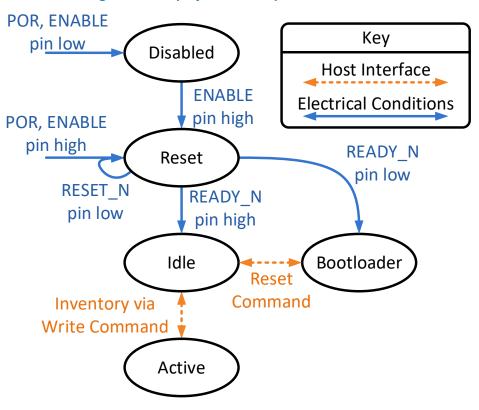

| 3.7            | Power Modes                          |    |  |  |

| 4 Dev          | rice Control and Programming         | 38 |  |  |

| 4.1            | Reader Communication Protocol        |    |  |  |

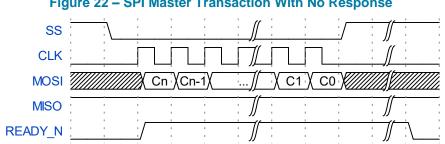

| 4.2            | SPI Digital Communication Interface  | 39 |  |  |

| 4.3            | Digital Input/Output Pins            |    |  |  |

| 5 Per          | formance Characteristics             |    |  |  |

| 5.1            | RX Sensitivity Summary               |    |  |  |

| 5.2            | Transmit Output Spectral Summary     |    |  |  |

| 5.3            | Transmit Power Control               | 40 |  |  |

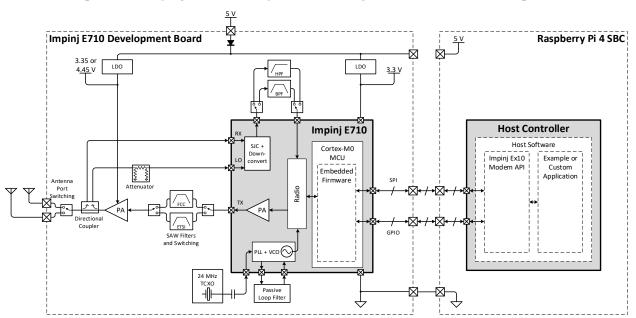

|                | inj E710 Development Board           | 40 |  |  |

| 7 Pac          | kage and Layout Information          | 42 |  |  |

| 7.1            | Package Dimensions                   |    |  |  |

| 7.2            | Package Markings                     | 43 |  |  |

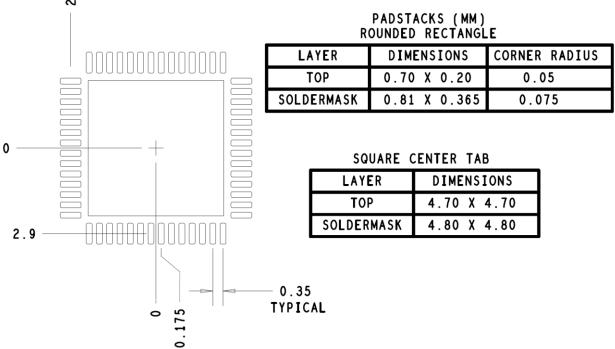

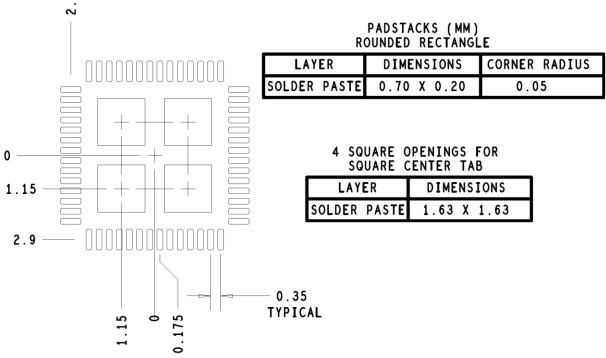

| 7. | 3 PCB Layout Recommendations                | .44 |

|----|---------------------------------------------|-----|

|    | 7.3.1 Recommended PCB Footprint             | .44 |

|    | 7.3.2 Additional PCB Layout Recommendations | .45 |

|    | 4 Recommended Reflow Profile                |     |

| 8  | Terminology                                 | .47 |

| 9  | Reference Documents                         | 49  |

| 10 | Document Change Log                         | 50  |

|    | Notices                                     |     |

|    |                                             |     |

## **TABLE OF FIGURES**

| Figure 1 – Impinj Reader Chip-Based Circuit Block Diagram                     | i   |

|-------------------------------------------------------------------------------|-----|

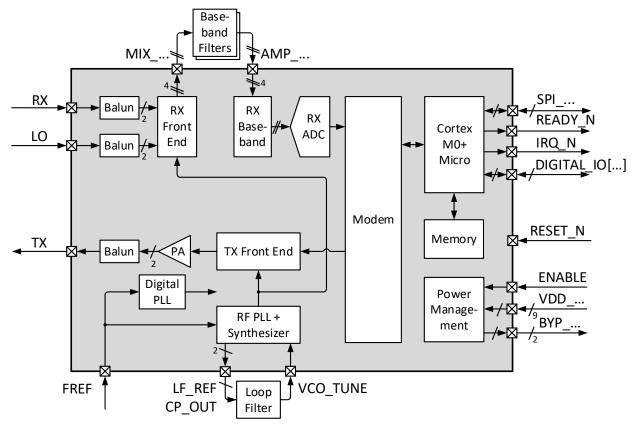

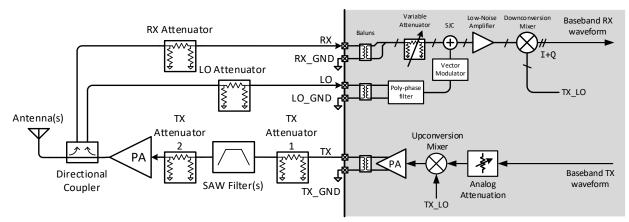

| Figure 2 – Impinj Reader Chip Detailed Internal Block Diagram                 |     |

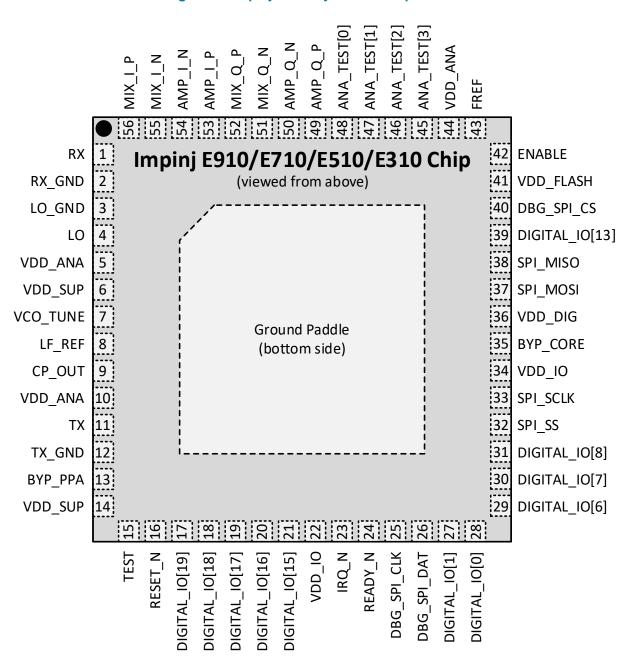

| Figure 3 – Impinj E Family Reader Chip Pinout                                 | 8   |

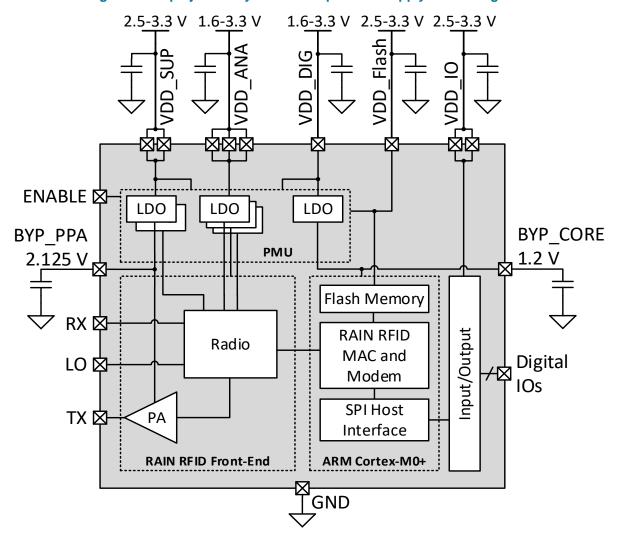

| Figure 4 – Impinj E Family Reader Chip Power Supply Block Diagram             | .12 |

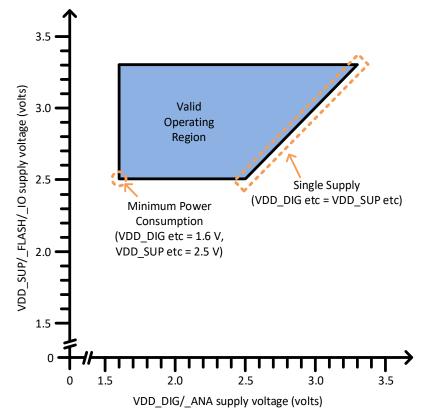

| Figure 5 – Impinj E Family Reader Chip Valid Power Supply Voltage Conditions  | .13 |

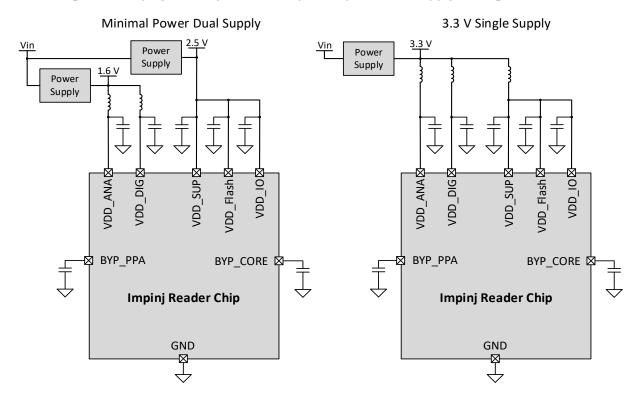

| Figure 6 – Impinj E Family Reader Chip Example Power Supply Configurations    | .13 |

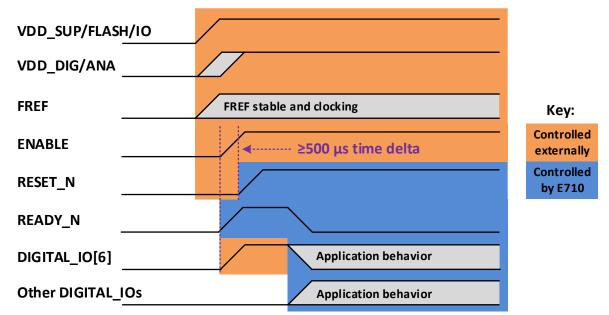

| Figure 7 – Impinj E Family Reader Chip Startup Power Supply and IO Sequencing | .15 |

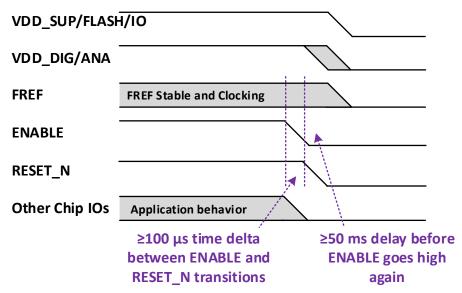

| Figure 8 – Impinj E Family Reader Chip Power Down Sequence                    | .16 |

| Figure 9 – Impinj E Family Reader Chip Disable-Enable Sequence                |     |

| Figure 10 – Transmitter Front End Analog Circuitry                            |     |

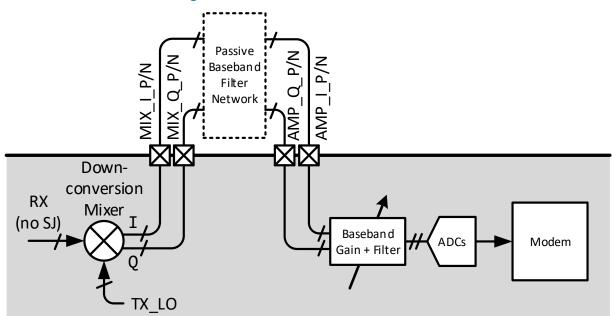

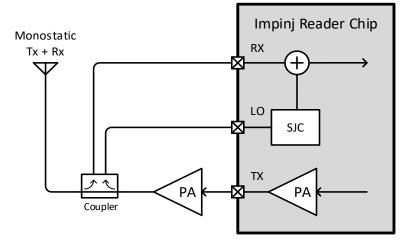

| Figure 11 – Receiver Front End Analog Circuitry                               |     |

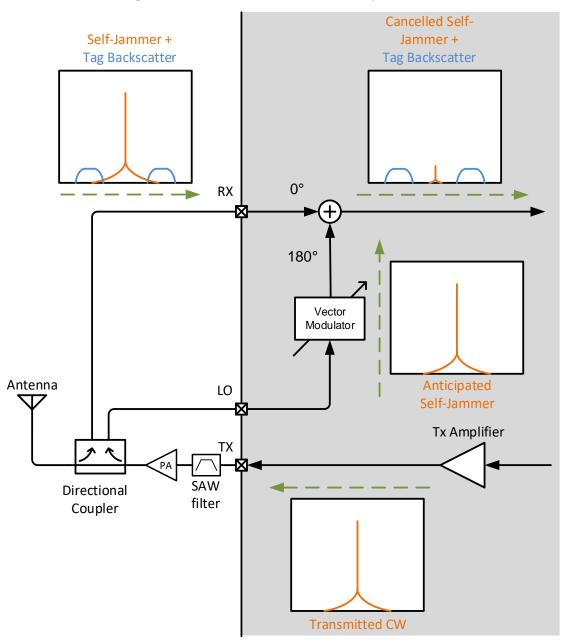

| Figure 12 – Self Jammer Cancellation Spectrum                                 |     |

| Figure 13 – Receive Baseband Interface                                        |     |

| Figure 14 – Receiver Baseband Filter Pin Interface Detail                     |     |

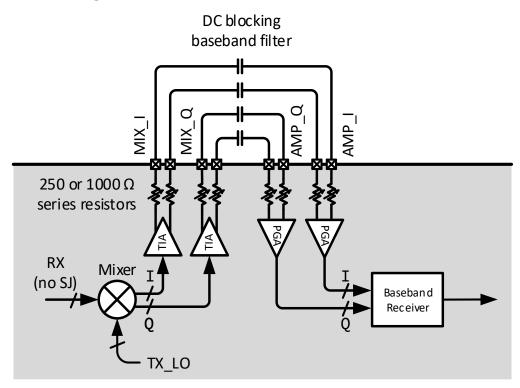

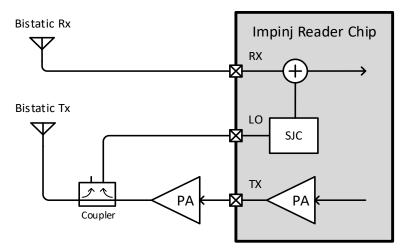

| Figure 15 – Monostatic Antenna Configuration                                  |     |

| Figure 16 – Bistatic Antenna Configuration                                    |     |

| Figure 17 – Multiple Monostatic Antennas With RF Switch                       |     |

| Figure 18 – RF Front End Block Diagram                                        |     |

| Figure 19 – Impinj Reader Circuit Block Diagram With Sensors                  |     |

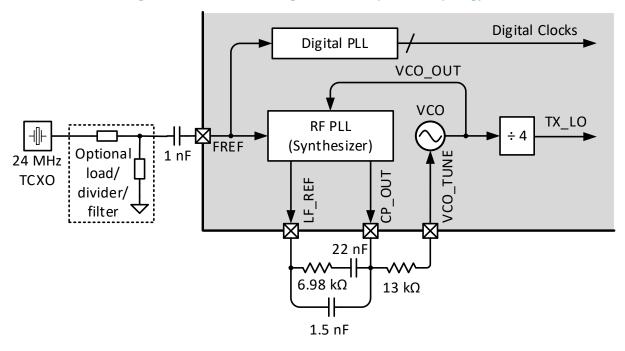

| Figure 20 – PLL Block Diagram and Loop Filter Topology                        |     |

| Figure 21 – Impinj Reader Chip Power Modes                                    |     |

| Figure 22 – SPI Master Transaction With No Response                           |     |

| Figure 23 – Impinj E710 Development Board System Detailed Block Diagram       |     |

| Figure 24 – Impinj Reader Chip Package and Pin Dimensions                     |     |

| Figure 25 – Impinj Reader Chip Package Markings                               |     |

| Figure 26 – Recommended PCB Footprint Pad and Soldermask Dimensions           |     |

| Figure 27 – Recommended PCB Footprint Solder Paste Dimensions                 | .45 |

## **TABLE OF TABLES**

| Table 1: Impinj E910, E710, E510, and E310 Reader Chips Overview    | i   |

|---------------------------------------------------------------------|-----|

| Table 2: Specification Documents                                    | 6   |

| Table 3: Impinj E Family Reader Chip Pin Signal Listing             | 9   |

| Table 4: Impinj E Family Reader Chip Digital IO Default Drive Modes | .10 |

| Table 5: Impinj E Family Reader Chip Host Device Connections        | .11 |

| Table 6: Absolute Minimum and Maximum Ratings                       | .18 |

| Table 7: Chip Operating Conditions                                  | .18 |

| Table 8: Chip Power Consumption                                     |     |

| Table 9: Chip Typical Current Consumption Distribution              | .19 |

| Table 10: RAIN Gen2 Inventory Round Reader Mode IDs and Parameters  | .20 |

| Table 11: RAIN Gen2X Inventory Round Reader Mode IDs and Parameters | .20 |

| Table 12: Impinj E Family Reader Mode Read Rate Performance         | .21 |

| Table 13: Sensitivity Test Antenna Conditions                       |     |

| Table 14: Impinj E910 RAIN Gen2 Receive Sensitivity At Chip Rx Pin  | .23 |

| Table 15: Impini E710 RAIN Gen2 Receive Sensitivity At Chip Rx Pin  | .23 |

| Table 16: Impinj E510 RAIN Gen2 Receive Sensitivity At Chip Rx Pin  |     |

|                                                                     |     |

| Table 17: Impinj E310 RAIN Gen2 Receive Sensitivity At Chip Rx Pin | 5 |

|--------------------------------------------------------------------|---|

|                                                                    |   |

| Table 19: Chip Transmitter Specifications                          | 6 |

| Table 20: Chip Power Detectors                                     |   |

| Table 21: Chip Transmit Synthesizer                                | 7 |

| Table 22: Chip Auxiliary ADC Specifications                        | 7 |

| Table 23: Chip Auxiliary DAC Specifications                        | 8 |

| Table 24: Chip Memory Specifications                               | 8 |

| Table 25: Chip Digital IO Specifications                           | 8 |

| Table 26: Chip Host SPI Interface Specifications                   | 8 |

| Table 27: Impini E Family Reader Chip Package Markings Encoding    |   |

| Table 28: Recommended Reflow Profile Parameters                    |   |

| Table 29: Relevant Terminology                                     |   |

| Table 30: Reference Documents                                      |   |

| Table 31: Document Change Log5                                     |   |

## **1 INTRODUCTION**

The Impinj E Family, consisting of Impinj E910, E710, E510, and E310 RAIN reader chips, provides a comprehensive portfolio of highly integrated systems-on-chips spanning a range of performance and price points. The E Family reader chips enable device OEMs to design a wide range of smart edge devices with embedded RAIN read/write capability. The reader chips deliver exceptional readability, inventory speed, range, decluttering, and data and privacy protection for identifying, locating, and authenticating next-generation, universal RAIN tags.

The E Family reader chips are designed for the RAIN radio standard (EPC Gen2 / ISO18000-63). They also support Impinj Gen2X<sup>™</sup>, an enhancement to the RAIN standard's radio and logical layers that can speed inventory, increase tag read range, declutter the environment, protect consumers, inhibit label and item counterfeiting, and reduce solution cost. Gen2X interoperates seamlessly with Gen2 / ISO 18000-63.

With 50% lower chip power consumption than the previous generation Impinj Indy series, the E Family reader chips support the design requirements for battery-powered, energy-efficient IoT devices embedding RAIN read/write capability. Additionally, the highly integrated E Family reader chips enable up to 80% smaller RAIN system designs than the Impinj Indy family, making them ideal for small, next-generation IoT devices. The E Family reader chips are also software- and pin-compatible, enabling easy performance upgrades and design reuse across various IoT devices. A broad portfolio of pre-certified modules available from the Impinj Partner Network reduces development complexity and accelerates the timeline of product development for next-generation IoT devices with RAIN read/write capability.

## 1.1 Impinj E Family Features Summary

E Family reader chips are highly integrated systems-on-chips containing all the RF and baseband blocks to interrogate and receive data from compatible RAIN tags, and an integrated microcontroller with embedded RAIN firmware providing the GS1 UHF Gen2 RAIN protocol as a pre-integrated feature. The reader chips implement direct conversion receiver architecture and operate in the worldwide UHF industrial, science, and medical (ISM) band.

E Family reader chips are a key element of the <u>Impini platform</u>, a foundation for RAIN solutions. They support Impini Gen2X Performance<sup>™</sup> enhancements that improve reader sensitivity, increase inventory speed, improve tag power delivery, declutter tag populations, and reliably filter those populations while reducing cost. E Family reader chips also support Impini Gen2X Protection<sup>™</sup> enhancements that protect tag data, authenticate tag chips, and protect consumer privacy.

### 1.1.1 Impinj E Family Systems-on-Chips Integration Features

- Modem architecture uses modern digital signal processing

- Self-jammer cancellation (SJC) technology

- Fully integrated voltage-controlled oscillator (VCO) with worldwide RAIN coverage

- Integrated Power Amplifier (PA) and baluns

- High compression point quadrature down-converting mixer

- Integrated radio-frequency (RF) power detectors for forward- and reverse-power sensing

- Integrated Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs)

- Configurable digital baseband

- Integrated ARM Cortex-M0+ microcontroller core with embedded firmware

- Host Serial Peripheral Interface (SPI) clocked at up to 4 MHz

- Impinj reader chip SDK including host library source code in C and code examples in C and python

#### 1.1.2 Impinj E Family Gen2X Performance Enhancements

E Family reader chips operate seamlessly in Gen2 or Gen2X inventory rounds using the reader modes described further in Section 2.4.4. Gen2X improves tag readability, especially for small tags on densely packed items. In mixed tag populations, E Family-based readers alternate Gen2 and Gen2X inventory rounds to read all tags. Regardless of the population mix, Gen2X consistently improves solution performance. When operating in Gen2X inventory rounds, the E Family reader chips boast improved:

- **Receive sensitivity**: Improved Gen2X preamble, backscatter modulation, pilot tone, and symbol encoding improve receive sensitivity across all E Family SKUs by 3 5 dB.

- **Inventory speed:** Configurable Gen2X RN16 parameters accelerate inventory by reducing ACK data and erroneous ACKs. Impinj TagFocus<sup>™</sup>, available in both Gen2 and Gen2X inventory rounds, allows a reader to reduce re-inventory time and focus on new tags.

- **Power delivery:** Powerup waveform shaping and extended Tari values allow E Family-based readers to deliver more power to tags, improving tag sensitivity up to 2 dB in both Gen2 and Gen2X inventory rounds.

- **Tag decluttering:** Session-dependent Gen2X RN16 protection allows E Family-based readers to discriminate which reader a tag's response is intended for, reducing cross-reads in multi-reader environments. Session-flag Booleans, available in both Gen2 and Gen2X inventory rounds, provide E Family-based readers with advanced tag decluttering techniques.

- **Tag filtering:** Tag selection during Gen2X inventory-round initiation ensures only tags-of-interest participate. Configurable Gen2X inventory responses (TID or EPC) allow TID-based solutions.

Full support for these Gen2X Performance enhancements is available with Impinj Reader Chip SDK+FW version 2.1 or later. This document includes some details on Gen2X Performance but does not detail the entirety of how to make use of these enhancements. For more information on utilizing Gen2X Performance, please request support through the Impinj Support Portal at <u>support.impinj.com</u>.

#### 1.1.3 Impinj E Family Gen2X Protection Enhancements

E Family reader chips support Gen2X protection features to protect tag data, enable authentication, and protect consumer privacy. These protection features are part of Gen2X Protection but are also available during Gen2 inventory rounds.

- **Protecting tag data:** The E Family reader chips include support for Impinj Integra<sup>™</sup> memory integrity checks for supporting tag chips that prevent tags sending a corrupted EPC, as well as a reader command that validates the data stored in memory on supporting tag chips.

- Authenticating tag chips: The E Family reader chips include support for dynamic, ISO 29167-11 authentication that, together with the <u>Impinj</u> Authentication <u>Service</u>, enables cryptographic authentication of supporting tag chips. Support for Impinj FastID<sup>™</sup> enables rapid EPC+TID inventory and EPC ⇔ TID verification (Gen2 only). Support for Impinj Protected Mode<sup>™</sup> (PIN-protected reversible kill) inhibits fraudulent product returns.

- **Protecting privacy:** E Family reader chips support Protected Mode. Protected Mode protects consumer privacy by configuring a supporting tag to be nonresponsive to a reader unless the reader first provides a correct PIN. Support for short-range mode reduces tag read range by roughly 10 times (20 dB).

Full support for these Gen2X Protection enhancements is available with Impinj Reader Chip SDK+FW version 2.0 or later. This document includes some details on Gen2X Protection but does not detail the entirety of how to make use of these enhancements. For more information on utilizing Gen2X Protection, please request support through the Impinj Support Portal at <u>support.impinj.com</u>.

### **1.2 Reference Documents**

The conventions used in the UHF Gen2 Specification (normative references, terms and definitions, symbols, abbreviated terms, and notation) were adopted in the drafting of this datasheet. Users of this datasheet should familiarize themselves with the <u>UHF Gen2 Specification</u>.

The Impinj E Family reader chips are fully compliant with the protocol specifications and local regulation documents in Table 2:

#### **Table 2: Specification Documents**

| Protocol Specification Documents                                                       | Local Regulation Documents                                                      |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| GS1 EPCGlobal Interoperability Test System for EPC<br>compliant Class-1 Gen-2 UHF RFID | <ul> <li>FCC 47 CFR Ch. 1, part 15</li> <li>ETSI EN 302 208-1 v2.1.1</li> </ul> |

## 1.3 Block Diagram

Figure 2 contains a detailed internal block diagram of the Impinie E Family reader chips. The architecture is based on direct conversion for both the transmitter and receiver.

## **2 SPECIFICATIONS**

## 2.1 Pin Listing and Signal Definitions

The Impinj E Family reader chips are offered in a 56-pin 6x6 mm QFN package. They require an external SAW filter and directional coupler in most configurations to implement a full radio circuit, along with a power amplifier (PA) if higher transmit power is required. The pinout for the 6x6 mm QFN is shown graphically in Figure 3 and in a list in Table 3. For package dimensions, see section 7.1 - Package Dimensions.

Figure 3 – Impini E Family Reader Chip Pinout

Note: Diagram not to scale

### Table 3: Impinj E Family Reader Chip Pin Signal Listing

| Pin # | Pin Name                   | Туре           | Description                                                                                   |

|-------|----------------------------|----------------|-----------------------------------------------------------------------------------------------|

| 1     | RX                         | RF In          | RFID receive signal                                                                           |

| 2     | RX_GND                     | RF Ground      | RFID receive signal ground                                                                    |

| 3     | LO_GND                     | RF Ground      | RFID local oscillator/self-jammer cancellation reference signal ground                        |

| 4     | LO                         | RF In          | RFID local oscillator/self-jammer cancellation reference signal                               |

| 5     | VDD_ANA                    | Power Supply   | Analog power supply                                                                           |

| 6     | VDD_SUP                    | Power Supply   | Supervisory power supply                                                                      |

| 7     | VCO_TUNE                   | Analog Input   | VCO tuning input                                                                              |

| 8     | LF_REF                     | Analog Output  | PLL loop filter reference                                                                     |

| 9     | CP_OUT                     | Analog Output  | PLL charge pump output                                                                        |

| 10    | VDD_ANA                    | Power Supply   | Analog power supply                                                                           |

| 11    | ТХ                         | RF Out         | RFID transmit signal                                                                          |

| 12    | TX_GND                     | RF Ground      | RFID transmit signal ground                                                                   |

| 13    | BYP_PPA                    | Power Bypass   | Power amplifier power supply bypass                                                           |

| 14    | VDD_SUP                    | Power Supply   | Supervisory power supply                                                                      |

| 15    | TEST                       | DNU            | Reserved for Impinj usage. Should be tied to ground.                                          |

| 16    | RESET_N                    | Digital Input  | Chip reset signal (active low)                                                                |

| 17    | DIGITAL_IO[19]             | Digital IO     | Digital input/output                                                                          |

| 18    | DIGITAL_IO[18]             | Digital IO     | Digital input/output                                                                          |

| 19    | DIGITAL_IO[17]             | Digital IO     | Digital input/output                                                                          |

| 20    | DIGITAL_IO[16]             | Digital IO     | Digital input/output                                                                          |

| 21    | DIGITAL_IO[15]             | Digital IO     | Digital input/output                                                                          |

| 22    | VDD_IO                     | Power Supply   | Digital input/output power supply                                                             |

| 23    | IRQ_N                      | Digital Output | Interrupt signal output (active low)                                                          |

| 24    | READY_N                    | Digital IO     | Host SPI interface slave ready signal output (active low), boot to application/bootloader pin |

| 25    | DBG_SPI_CLK                | Digital Output | Debug SPI interface master clock (SPI out for FW troubleshooting)                             |

| 26    | DBG_SPI_DAT                | Digital Output | Debug SPI interface master MOSI (SPI out for FW troubleshooting)                              |

| 27    | DIGITAL_IO[1]              | Digital IO     | Digital input/output                                                                          |

| 28    | DIGITAL_IO[0]              | Digital IO     | Digital input/output                                                                          |

| 29    | STARTUP /<br>DIGITAL_IO[6] | Digital IO     | Digital input/output (must be pulled or driven high at startup)                               |

| 30    | DIGITAL_IO[7]              | Digital IO     | Digital input/output                                                                          |

| 31    | DIGITAL_IO[8]              | Digital IO     | Digital input/output                                                                          |

| 32    | SPI_SS                     | Digital Input  | Host SPI interface slave select (active low)                                                  |

| 33    | SPI_SCLK                   | Digital Input  | Host SPI interface clock                                                                      |

| 34    | VDD_IO                     | Power Supply   | Input/output power supply                                                                     |

| 35    | BYP_CORE                   | Power Bypass   | Core power supply bypass                                                                      |

| 36    | VDD_DIG                    | Power Supply   | Digital power supply                                                                          |

| 37    | SPI_MOSI                   | Digital Input  | Host SPI interface master output slave input                                                  |

| 38    | SPI_MISO                   | Digital Output | Host SPI interface master input slave output                                                  |

| Pin #  | Pin Name       | Туре           | Description                                                             |

|--------|----------------|----------------|-------------------------------------------------------------------------|

| 39     | DIGITAL_IO[13] | Digital IO     | Digital input/output                                                    |

| 40     | DBG_SPI_CS     | Digital Output | Debug SPI interface master chip select (SPI out for FW troubleshooting) |

| 41     | VDD_FLASH      | Power Supply   | Flash memory power supply                                               |

| 42     | ENABLE         | Digital Input  | Chip enable input                                                       |

| 43     | FREF           | Clock Input    | 24 MHz PLL reference clock signal                                       |

| 44     | VDD_ANA        | Power Supply   | Analog power supply                                                     |

| 45     | ANA_TEST[3]    | Analog IO      | Analog test signal                                                      |

| 46     | ANA_TEST[2]    | Analog IO      | Analog test signal                                                      |

| 47     | ANA_TEST[1]    | Analog IO      | Analog test signal                                                      |

| 48     | ANA_TEST[0]    | Analog IO      | Analog test signal                                                      |

| 49     | AMP_Q_P        | Analog Input   | Q post-mixer amplifier quadrature differential input (positive)         |

| 50     | AMP_Q_N        | Analog Input   | Q post-mixer amplifier quadrature differential input (negative)         |

| 51     | MIX_Q_N        | Analog Output  | Q mixer quadrature differential output (negative)                       |

| 52     | MIX_Q_P        | Analog Output  | Q mixer quadrature differential output (positive)                       |

| 53     | AMP_I_P        | Analog Input   | I post-mixer amplifier quadrature differential input (positive)         |

| 54     | AMP_I_N        | Analog Input   | I post-mixer amplifier quadrature differential input (negative)         |

| 55     | MIX_I_N        | Analog Output  | I mixer quadrature differential output (negative)                       |

| 56     | MIX_I_P        | Analog Output  | I mixer quadrature differential output (positive)                       |

| Paddle | GND            | GND            | Chip ground                                                             |

## 2.2 IO Connections and Configurations

The Impinj E Family reader chips have input and output pins that are used to configure the devices. A host device such as an MCU or an application processor can control and monitor these pins. This section enumerates the required, recommended, and optional connections, and gives notes on their states.

**Note:** Impinj E Family reader chip firmware versions 2.1 and earlier don't support using the DIGITAL\_IO pins as inputs. This feature may be added in a future firmware release.

#### 2.2.1 Digital IO Default Drive Modes

The Impinij E Family reader chip digital IOs start up in either a pull-up or pull-down drive mode. The DIGITAL\_IOs can be reconfigured using the reader chip firmware operations, but at startup, their drive modes will be as shown in Table 4. The IO pull-up and pull-down resistance is specified in Table 25.

| Pin #             | Pin Name       | Туре          | Default Drive Mode |

|-------------------|----------------|---------------|--------------------|

| 15                | TEST           | DNU           | Pull-down          |

| 16                | RESET_N        | Digital Input | Pull-up            |

| 17                | DIGITAL_IO[19] | Digital IO    | Pull-up            |

| 18                | DIGITAL_IO[18] | Digital IO    | Pull-up            |

| 19 DIGITAL_IO[17] |                | Digital IO    | Pull-up            |

| 20 DIGITAL_IO[16] |                | Digital IO    | Pull-up            |

| 21 DIGITAL_IO[15] |                | Digital IO    | Pull-up            |

| 27 DIGITAL_IO[1]  |                | Digital IO    | Pull-up            |

| 28 DIGITAL_IO[0]  |                | Digital IO    | Pull-up            |

#### Table 4: Impinj E Family Reader Chip Digital IO Default Drive Modes

| Р | 'in #                         | Pin Name       | Туре       | Default Drive Mode |

|---|-------------------------------|----------------|------------|--------------------|

|   | 29 STARTUP /<br>DIGITAL_IO[6] |                | Digital IO | Pull-up            |

| ; | 30 DIGITAL_IO[7]              |                | Digital IO | Pull-up            |

|   | 31 DIGITAL_IO[8]              |                | Digital IO | Pull-up            |

| : | 39                            | DIGITAL_IO[13] | Digital IO | Pull-up            |

## 2.2.2 Host IO Connections

#### Table 5: Impinj E Family Reader Chip Host Device Connections

| Category                     | Pin Name | Туре              | Connection  | Notes                                                                                                                                                                                                                                                                         |  |

|------------------------------|----------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              | SPI_SS   | Digital<br>Input  | Required    | SPI slave select (active low)<br>Required for SPI communication with the host.                                                                                                                                                                                                |  |

|                              | SPI_SCLK | Digital<br>Input  | Required    | SPI clock<br>Required for SPI communication with the host.                                                                                                                                                                                                                    |  |

| SPI<br>(Serial<br>Peripheral | SPI_MOSI | Digital<br>Input  | Required    | SPI master output slave input<br>Required for SPI communication with the host.                                                                                                                                                                                                |  |

| Interface)                   | SPI_MISO | Digital<br>Output | Required    | SPI master input slave output<br>Required for SPI communication with the host.                                                                                                                                                                                                |  |

|                              | READY_N  | Digital IO        | Required    | SPI slave ready signal output (active low), startup boot to application/bootloader pin Required for SPI communication with the host.                                                                                                                                          |  |

| Reader<br>Chip<br>Control    | ENABLE   | Digital<br>Input  | Required    | Chip enable input<br>Allows host to control startup and put chip in a low power mode.<br>Details on control below.                                                                                                                                                            |  |

|                              | RESET_N  | Digital<br>Input  | Required    | Chip reset signal (active low)<br>Allows host to reset the reader chip without cycling the power.<br>Must be sequenced as described in the next section.<br>The reader chip drives this signal strong low during startup, so it<br>must not be driven strong high externally. |  |

| Firmware<br>State            | IRQ_N    | Digital<br>Output | Recommended | Interrupt signal output (active low)<br>Indicates to the host when data is ready on the reader chip. Can<br>be left unconnected if host queries the reader chip regularly.                                                                                                    |  |

#### 2.2.3 IO conditions

Certain Impinj E Family reader chip IOs must be in a specific electrical state for specific optional or mandatory operational states. They are listed below. These are in addition to the power supply pins, synthesizer pins, RF and baseband interface pins, etc. More details on startup sequence timing are shown in section 2.3.1 - Power Up Sequence.

ENABLE must be driven high to enable the reader chip. It should only be driven high after a stable 24 MHz clock signal is present at the FREF pin. ENABLE may be driven low to put the part into "Shutdown" mode, as described in section 3.7 - Power Modes.

RESET\_N must be allowed to be driven low by the reader chip entering startup. If it is driven low to reset the part, it must be released >500 µs after the ENABLE pin is driven high. An internal pull-up resistor will pull the pin high. RESET\_N may be used to reset the reader chips during operation.

DIGITAL\_IO[6] must be driven high during reader chip firmware startup (after the RESET\_N pin goes high, and before the READY\_N pin goes low). This may be accomplished either by controlling the DIGITAL\_IO[6] pin using a host device, or by applying a strong high or pullup voltage to the pin. If a pullup is applied, the pin can be reconfigured as a strong drive by the reader chip and used to drive an external signal after startup is complete. On the Impinj E710 development board, this pin is pulled high with a 10 k $\Omega$  resistor.

READY\_N must be driven strong low for 8706 FREF clock cycles (~362.75 µs) at startup (after the ENABLE pin goes high) to force the reader chip into bootloader mode. After a normal startup to application (not to bootloader) the READY\_N pin will be driven low by E710 to indicate that startup has completed, and the reader chip is ready to communicate with the host via the SPI. Interface. The READY\_N pin is also part of the SPI signaling wireline, as described in section 4.2 - SPI Digital Communication Interface.

## 2.3 Power Supply

The Impinj E Family reader chips have multiple power supply pins, and to achieve maximum performance, they must be properly configured. A block diagram of the reader chip's power supplies, their ranges, and the circuits they drive is shown in Figure 4.

VDD\_SUP, VDD\_IO, and VDD\_FLASH must all be powered at the same voltage, within the range of 2.5 to 3.3 volts. VDD\_ANA and VDD\_DIG must be powered at the same voltage, within the range of 1.6 to 3.3 volts, and lower than or equal to the VDD\_SUP voltage. Note that these values are nominal, and the actual maximum and minimum values have additional margin, as shown in Table 7.

All the supplies may share the same voltage, as long as it is within the shared range of 2.5 to 3.3 volts. Power consumption is optimized when each of the supplies are at their lowest allowed voltage (e.g. 1.6 volts for VDD\_ANA and VDD\_DIG, and 2.5 volts for VDD\_SUP, VDD\_IO, and VDD\_FLASH). The valid range of supply voltage combinations is shown in Figure 5, and examples of both minimal power dual supply and a 3.3 V single supply are shown in Figure 6. Ferrite beads are used for isolation of the power supplies. These

diagrams are simplifications, and both passive and active isolation of the power supplies can improve performance. See the Impini E710 Development Board Application Note for more details.

Figure 6 – Impinj E Family Reader Chip Example Power Supply Configurations

The supply pins must be bypassed with external bypass capacitors, which will also filter power supply noise. See the <u>Impini E710 Development Board Application Note</u> for an example implementation. The individual bypass capacitors should be placed close to the pins that they are bypassing. When an array of bypass capacitors is shown on the same net connecting multiple power pins, the array should be split up physically such that each pin has its own bypass capacitor.

BYP\_PPA and BYP\_CORE are not power supply inputs, but rather external bypass pins for the internally regulated power supplies. They should be externally bypassed with capacitance, but not driven. External bypass capacitance must be 10  $\mu$ F or above, as demonstrated in the Impinj E710 development board. No external loads should be placed on these supply voltages. BYP\_CORE is regulated to 1.2 V nominal. BYP\_PPA is regulated to 2.125 V nominal. The un-bypassed, internal only analog supply BYP\_ANA is regulated to 1.2 V nominal.

All of the duplicated power supplies (e.g. pins 6 and 14, both connected to VDD\_SUP, see also VDD\_ANA and VDD\_IO) must be connected external to the reader chip.

For more details on potential external power supply implementations, see the <u>Impini E710 Development</u> <u>Board Application Note</u>.

#### 2.3.1 Power Up Sequence

The Impinities Family reader chips must be powered up using a specific sequence of conditions on the power supplies, IOs, and other pins. This sequence is described verbally in the paragraph below, in a numbered list format following that, and graphically in Figure 7.

The power-up sequence must start by powering the VDD\_SUP, VDD\_IO, and VDD\_FLASH supplies. The VDD\_DIG and VDD\_ANA power supplies may be powered at the same time or after the VDD\_SUP, VDD\_IO, and VDD\_FLASH supplies. To reiterate, the VDD\_DIG and VDD\_ANA supplies must not be powered up before the other power supplies on the device. A 24 MHz clock must be present at FREF for the part to start up successfully. The part will not startup if the ENABLE pin is not high, or if the RESET\_N pin is not allowed to be driven low by the reader chip. Approximately 500 µs after the enable pin goes high, the part will release the RESET\_N pin, and firmware startup will begin. DIGITAL\_IO[6] must be pulled or driven strong high during firmware startup, and then may be used as a digital input or output per application requirements. The READY\_N pin will be driven low by the reader chip when firmware startup has completed, and the part is ready to communicate via SPI with the host device. The READY\_N pin may also be driven low when RESET\_N is released during startup to force the part into the bootloader mode. For more details on this, see section 2.2.3 - IO conditions.

This startup sequence is implemented in the Impinj reader chip SDK, specifically in **power\_transactor.c** API **ex10\_power\_up\_to\_application(...)**.

For more detail on startup, including detail on how to boot to the bootloader, see the firmware HTML documentation in the <u>Impini Ex10 Reader Chip SDK Specification</u>.

- 1. Power the reader chip

- a. VDD\_SUP, VDD\_FLASH, and VDD\_IO should be powered up before or simultaneously with VDD\_DIG and VDD\_ANA

- b. A 24 MHz clock signal should be applied to FREF simultaneously or after power is applied

- 2. ≥5 ms after powering the chip, apply initial IO conditions to startup the reader chip

- a. RESET\_N must be driven low by the host

- b. DIGITAL\_IO[6] should be pulled high by the host

- c. ENABLE should be driven high by the host

- d. All other IOs should be left floating

- 3. ≥10 ms after applying initial IO conditions, apply final IO conditions to startup the reader chip

- a. RESET\_N should be released by the host

- b. After approximately 500 μs, the RESET\_N pin will be driven high by the reader chip, and firmware startup will begin

- 4. Observe the conclusion of startup

- a. When the READY\_N pin is driven low by the reader chip, firmware startup has completed

- b. At this point, the reader chip firmware will respond to SPI commands, and all the DIGITAL\_IOs can be used for other purposes

- c. The ENABLE pin should still be driven high, and RESET\_N should be left floating during operation

#### Figure 7 – Impinj E Family Reader Chip Startup Power Supply and IO Sequencing

#### 2.3.2 Power Down Sequence

The Impinj E Family reader chips must be powered down in a specific sequence. That sequence is described in detail below and shown in Figure 8.

- 1. Disable the reader chip

- a. The reader chip can be disabled by driving the ENABLE pin low

- i. At this point, the reader chip will stop responding to SPI communication, and application driven IO behaviors will cease

- b. The ENABLE pin must be driven low for 100  $\mu s$  before the reader chip is reset or powered down

- i. The FREF input must continue clocking until this 100 µs delay has completed

- 2. Reset and power down the reader chip

- a. All chip IOs should either be left floating(high impedance) or driven to ground

- b. FREF may stop clocking

- c. The RESET\_N pin may be driven low

- d. The VDD pins may be driven low, which will also drive RESET\_N low if it is floating

- i. VDD\_DIG and VDD\_ANA should be driven low either before or simultaneously with VDD\_SUP, VDD\_FLASH, and VDD\_DIG

- 3. The reader chip should be left powered down for at least 50 ms before it is powered up again

#### 2.3.3 Disable-Enable Sequence

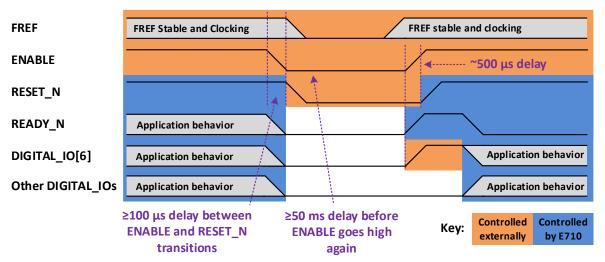

The Impinj E Family reader chips must be disabled and re-enabled in a specific sequence. That sequence is described in detail below and shown in Figure 9.

The Disable functionality allows reduced power consumption without removing power from the reader chip. Reader designs should still maintain the ability to power down the reader chip to resolve unrecoverable states.

**Note:** It is critical that the ENABLE pin goes low 100 µs before RESET\_N transitions low. If this condition is not met, the reader chip could enter a state that is only recoverable through a chip power cycle.

- 1. Drive the enable pin low

- a. The reader chip should be disabled by driving the ENABLE pin low

- i. At this point, the reader chip will stop responding to SPI communication, and application driven IO behaviors will cease

- b. The ENABLE pin must be driven low for 100  $\mu$ s before the RESET\_N pin is driven low

- i. The FREF input must continue clocking until this 100  $\mu$ s delay has completed

- 2. Reset the reader chip

- a. All chip IOs should either be left floating (high impedance) or driven to ground

- b. FREF may stop clocking

- c. The RESET\_N pin should be driven low

- 3. Chip disabled

- a. At this point, the reader chip is disabled, and will consume reduced current

- b. The reader chip must be left disabled for at least 50 ms before it is enabled again

- 4. After ~5 ms, Apply initial IO conditions to startup the reader chip

- a. RESET\_N must be driven low by the host

- b. DIGITAL\_IO[6] should be pulled high by the host

- c. ENABLE should be driven high by the host

- d. All other IOs should be left floating

- 5. After ~10 ms, apply final IO conditions to startup the reader chip

- a. RESET\_N should be released by the host

- b. After approximately 500  $\mu s,$  the RESET\_N pin will be driven high by the reader chip, and firmware startup will begin

- 6. Observe the conclusion of startup

- a. When the READY\_N pin is driven low by the reader chip, firmware startup has completed

- b. At this point, the reader chip firmware will respond to SPI commands, and all of the DIGITAL\_IOs can be used for other purposes

- c. The ENABLE pin should still be driven high, and RESET\_N should be left floating during operation

Figure 9 – Impinj E Family Reader Chip Disable-Enable Sequence

## 2.4 Electrical Specifications

#### 2.4.1 Absolute Maximum Ratings

The absolute maximum ratings in Table 6 define the limitations for electrical and thermal stresses. These limits prevent permanent damage to the Impinj E Family reader chips. If the reader chip is exposed to conditions outside of these ranges, it is no longer guaranteed to operate properly or meet the performance specifications listed in this document, even after conditions return to the valid ranges.

| Parameter                          | Min          | Max             | Unit     | Conditions                                                                    |

|------------------------------------|--------------|-----------------|----------|-------------------------------------------------------------------------------|

| VDD_SUP/_FLASH/_IO voltage         | -0.3         | 3.6             | volts DC |                                                                               |

| VDD_DIG/_ANA voltage               | -0.3         | 3.6             | volts DC |                                                                               |

| Chip IO applied voltage            | GND<br>- 0.5 | VDD_IO<br>+ 0.5 | volts DC | Under typical conditions, IO voltages should not go below GND or above VDD_IO |

| ESD Bower ownels and IO ning       | N/A          | N/A             | N/A      | HBM Class 3A                                                                  |

| ESD, Power supply and IO pins      | N/A          | N/A             | N/A      | CDM Class C0b                                                                 |

| ESD DE nine                        | N/A          | N/A             | N/A      | HBM Class 2                                                                   |

| ESD, RF pins                       | N/A          | N/A             | N/A      | CDM Class C0b                                                                 |

| TX, LO, RX port RF input power     | N/A          | +20             | dBm      | Note: Optimal RF performance achieved at lower power levels, see Table 18     |

| Storage Temperature                | -55          | 125             | °C       |                                                                               |

| Case Temperature                   | N/A          | 260             | °C       | For reflow purposes                                                           |

| Package Moisture Sensitivity Level | N/A          | N/A             | N/A      | Moisture Sensitivity Level (MSL) 3                                            |

#### **Table 6: Absolute Minimum and Maximum Ratings**

#### 2.4.2 Operating Conditions

The operating conditions listed in this section describe the conditions under which the Impinj E Family reader chips will operate properly and meet the performance specifications listed in this document. If these conditions are not met, the reader chip will not perform as expected, but will also not suffer permanent damage.

| Parameter                                                | Min   | Тур              | Max   | Unit     | Conditions                                                                                                                        |

|----------------------------------------------------------|-------|------------------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| VDD_SUP/_FLASH/_IO voltage                               | 2.375 | 2.5 or 3.3       | 3.465 | volts DC | All supplies in this row must be<br>operated at the same voltage<br>Typ column lists common voltages                              |

| VDD_DIG/_ANA voltage                                     | 1.52  | 1.6, 2.5, or 3.3 | 3.465 | volts DC | All supplies in this row must be<br>operated at the same voltage<br>VDD_DIG must be ≤ VDD_SUP<br>Typ column lists common voltages |

| Operating Ambient Temperature                            | -40   | N/A              | 85    | °C       | Analysis performed using worst case power consumption, the $\theta_{JA}$ PCB layout and conditions                                |

| Junction Temperature                                     |       | N/A              | 125   | °C       |                                                                                                                                   |

| Junction to Ambient Thermal Resistance ( $\theta_{JA}$ ) |       | 27.8             |       | °C/W     | Typical 4-layer PCB layout, 9 vias<br>below e-pad, no heat sink, no<br>forced airflow                                             |

#### **Table 7: Chip Operating Conditions**

## 2.4.3 Power Supply Specifications

#### **Table 8: Chip Power Consumption**

| Parameter                   | Min | Тур | Max  | Unit | Conditions              |

|-----------------------------|-----|-----|------|------|-------------------------|

| Chip performing inventory,  | N/A | 950 | 1065 | mW   | 3.3 V Single Supply     |

| transmitting at +11 dBm     | N/A | 700 | 800  | mW   | 2.5 V Single Supply     |

| Note: SJC does not increase | N/A | 650 | 750  | mW   | 3.3 / 1.6 V Dual Supply |

| power consumption.          | N/A | 550 | 650  | mW   | 2.5 / 1.6 V Dual Supply |

| Chip idle                   | N/A | 48  | 75   | mW   | 3.3 V Single Supply     |

| (chip powered with firmware | N/A | 38  | 60   | mW   | 2.5 V Single Supply     |

| executing, but without host | N/A | 30  | 46   | mW   | 3.3 / 1.6 V Dual Supply |

| configuration performed)    | N/A | 28  | 44   | mW   | 2.5 / 1.6 V Dual Supply |

| Chip disabled               | N/A | 0.4 | 0.5  | mW   | 3.3 V Single Supply     |

|                             | N/A | 0.1 | 0.2  | mW   | 2.5 V Single Supply     |

|                             | N/A | 0.3 | 0.4  | mW   | 3.3 / 1.6 V Dual Supply |

|                             | N/A | 0.1 | 0.2  | mW   | 2.5 / 1.6 V Dual Supply |

| Chip held in reset          | N/A |     | 50   | mW   | Using RESET_N pin       |

#### Table 9: Chip Typical Current Consumption Distribution

|                                             | VDD_ANA                                                 | VDD_DIG        | VDD_FLASH          | VDD_IO      | VDD_SUP | Units |  |  |  |  |  |

|---------------------------------------------|---------------------------------------------------------|----------------|--------------------|-------------|---------|-------|--|--|--|--|--|

|                                             | Power                                                   | r Supply Cond  | ition: Single Supp | ly 3.3 V    |         |       |  |  |  |  |  |

| Supply Voltage                              | 3.3                                                     | 3.3            | 3.3                | 3.3         | 3.3     | volts |  |  |  |  |  |

| Chip Active                                 | 133.8                                                   | 34.3           | 0.0                | 0.1         | 115.0   | mA    |  |  |  |  |  |

| Chip Idle                                   | 0.4                                                     | 10.2           | 0.0                | 0.1         | 3.8     | mA    |  |  |  |  |  |

| Chip Disabled                               | 0.0                                                     | 0.1            | 0.0                | 0.0         | 0.0     | mA    |  |  |  |  |  |

| Power Supply Condition: Single Supply 2.5 V |                                                         |                |                    |             |         |       |  |  |  |  |  |

| Supply Voltage                              | Voltage         2.5         2.5         2.5         2.5 |                |                    |             |         |       |  |  |  |  |  |

| Chip Active                                 | 133.0 33.6 0.0 0.0 115.3                                |                |                    |             |         | mA    |  |  |  |  |  |

| Chip Idle                                   | 0.4                                                     | 10.1           | 0.0                | 1.1         | 3.6     | mA    |  |  |  |  |  |

| Chip Disabled                               | 0.0                                                     | 0.0            | 0.0                | 0.0         | 0.0     | mA    |  |  |  |  |  |

|                                             | Power S                                                 | upply Conditic | n: Dual Supply 3.  | 3 V / 1.6 V |         |       |  |  |  |  |  |

| Supply Voltage                              | 1.6                                                     | 1.6            | 3.3                | 3.3         | 3.3     | volts |  |  |  |  |  |

| Chip Active                                 | 133.8                                                   | 34.3           | 0.0                | 0.1         | 115.0   | mA    |  |  |  |  |  |

| Chip Idle                                   | 0.4                                                     | 10.2           | 0.0                | 0.1         | 3.8     | mA    |  |  |  |  |  |

| Chip Disabled                               | 0.0                                                     | 0.1            | 0.0                | 0.0         | 0.0     | mA    |  |  |  |  |  |

|                                             | Power S                                                 | upply Conditio | n: Dual Supply 2.  | 5 V / 1.6 V |         |       |  |  |  |  |  |

| Supply Voltage                              | 1.6                                                     | 1.6            | 2.5                | 2.5         | 2.5     | volts |  |  |  |  |  |

| Chip Active                                 | 133                                                     | 33.6           | 0.0                | 0.0         | 115.3   | mA    |  |  |  |  |  |

| Chip Idle                                   | 0.4                                                     | 10.1           | 0.0                | 1.1         | 3.6     | mA    |  |  |  |  |  |

| Chip Disabled                               | 0.0                                                     | 0.0            | 0.0                | 0.0         | 0.0     | mA    |  |  |  |  |  |

Note: All values typical, rounded to the nearest tenth of a mA

## 2.4.4 Gen2 and Gen2X Reader Modes and Performance Specifications

The E Family reader chips operate seamlessly across Gen2 and Gen2X inventory rounds using the reader modes detailed in Table 10 and Table 11 below. To initiate a Gen2 inventory round, the E Family reader

chips send a Gen2 preamble followed by a *Query* command, and for a Gen2X inventory round, the E Family reader chip sends a Gen2X preamble followed by a *Scan* command. The reader controls whether subsequent inventory rounds are Gen2 or Gen2X by sending a *Query* or *Scan*, respectively. Supporting tag chips share session and select flag values across Gen2 and Gen2X inventory rounds, allowing seamless tag population management across Gen2 and Gen2X.

All other commands are the same between Gen2 and Gen2X, but the frame-syncs are different. Gen2 inventory rounds use a Gen2 frame-sync whereas Gen2X inventory rounds use a Gen2X frame-sync. When in a Gen2 inventory round, tag chips ignore commands with a Gen2X frame sync, and vice versa. All commands except *Query* and *Scan* are common between Gen2 and Gen2X inventory rounds – the only difference is the frame-sync.

For more details on Gen2X inventory rounds please request support through the Impinj Support Portal at <u>support.impinj.com</u>.

| FCC<br>Mode<br>ID | ETSI<br>LB<br>Mode<br>ID | ETSI<br>UB<br>Mode<br>ID | Supported<br>Regions* | Reader Mode<br>Optimization | Forward<br>Link<br>Modulation | Tari<br>(µs) | PIE | BLF<br>(kHz) | Back-<br>scatter<br>Link<br>Modulation |

|-------------------|--------------------------|--------------------------|-----------------------|-----------------------------|-------------------------------|--------------|-----|--------------|----------------------------------------|

| 103               | N/A                      | N/A                      | FCC                   | FCC Read Rate               | DSB-ASK                       | 6.25         | 1.5 | 640          | FM0                                    |

| 102               | N/A                      | 302                      | ETSI UB+              | ETSI UB Read<br>Rate        | PR-ASK                        | 7.5          | 2.0 | 640          | FM0                                    |

| 120               | N/A                      | N/A                      | FCC                   | FCC Hybrid                  | DSB-ASK                       | 6.25         | 1.5 | 640          | Miller M=2                             |

| 104               | N/A                      | N/A                      | FCC                   | FCC Read Rate               | DSB-ASK                       | 6.25         | 1.5 | 320          | FM0                                    |

| 124               | N/A                      | 323                      | ETSI UB+              | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 2.0 | 640          | Miller M=2                             |

| N/A               | 203                      | N/A                      | Japan+                | Japan Read<br>Rate          | PR-ASK                        | 12.5         | 1.5 | 426          | FM0                                    |

| N/A               | 202                      | N/A                      | ETSI LB+              | ETSI LB Read<br>Rate        | PR-ASK                        | 15           | 2.0 | 426          | FM0                                    |

| N/A               | 226                      | N/A                      | Japan+                | Japan Hybrid                | PR-ASK                        | 12.5         | 1.5 | 426          | Miller M=2                             |

| 147               | N/A                      | 344                      | ETSI UB+              | ETSI UB DRM                 | PR-ASK                        | 7.5          | 2.0 | 640          | Miller M=4                             |

| 148               | N/A                      | 345                      | ETSI UB+              | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 1.5 | 640          | Miller M=4                             |

| N/A               | 225                      | N/A                      | ETSI LB+              | ETSI LB Hybrid              | PR-ASK                        | 15           | 2.0 | 426          | Miller M=2                             |

| N/A               | 224                      | N/A                      | Japan+                | Japan Hybrid                | PR-ASK                        | 12.5         | 1.5 | 320          | Miller M=2                             |

| 125               | 223                      | 325                      | ETSI LB+              | ETSI LB Hybrid              | PR-ASK                        | 15           | 2.0 | 320          | Miller M=2                             |

| 123               | 222                      | 324                      | ETSI LB+              | ETSI LB Hybrid              | PR-ASK                        | 20           | 2.0 | 320          | Miller M=2                             |

| 141               | 241                      | 342                      | ETSI LB+              | ETSI LB DRM                 | PR-ASK                        | 20           | 2.0 | 320          | Miller M=4                             |

| 146               | 244                      | 343                      | ETSI LB+              | FCC DRM                     | PR-ASK                        | 20           | 2.0 | 250          | Miller M=4                             |

| N/A               | 205                      | N/A                      | ETSI LB+              | Japan Ultra-<br>DRM         | PR-ASK                        | 20           | 2.0 | 50           | FM0                                    |

| 185               | 285                      | 382                      | ETSI LB+              | Sensitivity                 | PR-ASK                        | 20           | 2.0 | 160          | Miller M=8                             |

#### Table 10: RAIN Gen2 Inventory Round Reader Mode IDs and Parameters

\*Supported Regions column indicates which regions a mode should pass regulatory certification tests on the Impinj E710 Development Board. The listed region is the most difficult region to pass, indicating that less difficult regions will also pass. For example, Mode 302 will pass ETSI upper band and FCC, but not Japan or ETSI lower band.

#### Table 11: RAIN Gen2X Inventory Round Reader Mode IDs and Parameters

| FCC<br>Mode<br>ID | ETSI<br>LB<br>Mode<br>ID | ETSI<br>UB<br>Mode<br>ID | Supported<br>Regions* | Reader Mode<br>Optimization | Forward<br>Link<br>Modulation | Tari<br>(µs) | PIE | BLF<br>(kHz) | Backscatter<br>Link<br>Modulation |

|-------------------|--------------------------|--------------------------|-----------------------|-----------------------------|-------------------------------|--------------|-----|--------------|-----------------------------------|

| 4124              | N/A                      | 4323                     | ETSI UB+              | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 2.0 | 640          | BPSK M=2                          |

| 4148              | N/A                      | 4345                     | ETSI UB+              | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 1.5 | 640          | BPSK M=4                          |

| 4123              | 4222                     | 4324                     | ETSI LB+              | ETSI LB Hybrid              | PR-ASK                        | 20           | 2.0 | 320          | BPSK M=2                          |

| FCC<br>Mode<br>ID | ETSI<br>LB<br>Mode<br>ID | ETSI<br>UB<br>Mode<br>ID | Supported<br>Regions* | Reader Mode<br>Optimization | Forward<br>Link<br>Modulation | Tari<br>(µs) | PIE | BLF<br>(kHz) | Backscatter<br>Link<br>Modulation |

|-------------------|--------------------------|--------------------------|-----------------------|-----------------------------|-------------------------------|--------------|-----|--------------|-----------------------------------|

| 4141              | 4241                     | 4342                     | ETSI LB+              | ETSI LB DRM                 | PR-ASK                        | 20           | 2.0 | 320          | BPSK M=4                          |

| 4146              | 4244                     | 4343                     | ETSI LB+              | FCC DRM                     | PR-ASK                        | 20           | 2.0 | 250          | BPSK M=4                          |

| 4185              | 4285                     | 4382                     | ETSI LB+              | Sensitivity                 | PR-ASK                        | 20           | 2.0 | 160          | BPSK M=8                          |

\*Supported Regions column indicates which regions a mode should pass regulatory certification tests on the Impinj E710 Development Board. The listed region is the most difficult region to pass, indicating that less difficult regions will also pass. For example, Mode 4345 will pass ETSI upper band and FCC, but not Japan or ETSI lower band.

#### 2.4.4.1 Inventory Read Rate Performance

Tag read rates for a large tag population in a quiet RF environment using Gen2 and Impinj Gen2X reader modes are shown in Table 12. Read rates for Impinj E910 reader chip are typically slightly higher, and Impinj E510 and E310 reader chips are typically lower. For more details, see the Impinj E710 Development Board Application Note. For information on selecting a Reader Mode, see the following support article: Selecting a Reader Mode for the Impinj Reader Chips.

Read rates for Gen2X reader modes with standard RN16 parameters are typically slightly lower than Gen2 reader modes with equivalent reader mode parameters. However, Gen2X link enhancements include configurable RN16 parameters, both numerical and error-reducing, that accelerate inventory by reducing ACK data and erroneous ACKs. They also include session-dependent RN16 protection that allows readers to discriminate which reader a tag's response is intended for, reducing cross-reads in multi-reader environments. For more details on Gen2X tag-to-reader link enhancements, please request support through the Impinj Support Portal at support.impinj.com.

| Reader<br>Mode<br>ID* | Reader Mode<br>Optimization | Forward<br>Link<br>Modulation | Tari<br>(µs) | PIE | BLF<br>(kHz) | Back-<br>scatter<br>Link<br>Modulation | Typical<br>Optimized<br>Read Rate<br>(tags/s) |

|-----------------------|-----------------------------|-------------------------------|--------------|-----|--------------|----------------------------------------|-----------------------------------------------|

| 103                   | FCC Read Rate               | DSB-ASK                       | 6.25         | 1.5 | 640          | FM0                                    | 1100                                          |

| 302                   | ETSI UB Read Rate           | PR-ASK                        | 7.5          | 2.0 | 640          | FM0                                    | 950                                           |

| 120                   | FCC Hybrid                  | DSB-ASK                       | 6.25         | 1.5 | 640          | Miller M=2                             | 800                                           |

| 104                   | FCC Read Rate               | DSB-ASK                       | 6.25         | 1.5 | 320          | FM0                                    | 725                                           |

| 323                   | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 2.0 | 640          | Miller M=2                             | 700                                           |

| 203                   | Japan Read Rate             | PR-ASK                        | 12.5         | 1.5 | 426          | FM0                                    | 600                                           |

| 202                   | ETSI LB Read Rate           | PR-ASK                        | 15           | 2.0 | 426          | FM0                                    | 500                                           |

| 226                   | Japan Hybrid                | PR-ASK                        | 12.5         | 1.5 | 426          | Miller M=2                             | 500                                           |

| 344                   | ETSI UB DRM                 | PR-ASK                        | 7.5          | 2.0 | 640          | Miller M=4                             | 450                                           |

| 345                   | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 1.5 | 640          | Miller M=4                             | 450                                           |

| 225                   | ETSI LB Hybrid              | PR-ASK                        | 15           | 2.0 | 426          | Miller M=2                             | 425                                           |

| 224                   | Japan Hybrid                | PR-ASK                        | 12.5         | 1.5 | 320          | Miller M=2                             | 400                                           |

| 223                   | ETSI LB Hybrid              | PR-ASK                        | 15           | 2.0 | 320          | Miller M=2                             | 350                                           |

| 222                   | ETSI LB Hybrid              | PR-ASK                        | 20           | 2.0 | 320          | Miller M=2                             | 300                                           |

| 241                   | ETSI LB DRM                 | PR-ASK                        | 20           | 2.0 | 320          | Miller M=4                             | 200                                           |

| 146                   | FCC DRM                     | PR-ASK                        | 20           | 2.0 | 250          | Miller M=4                             | 175                                           |

| 205                   | Japan Ultra DRM             | PR-ASK                        | 20           | 2.0 | 50           | FM0                                    | 95                                            |

| 285                   | Sensitivity                 | PR-ASK                        | 20           | 2.0 | 160          | Miller M=8                             | 70                                            |

Table 12: Impinj E Family Reader Mode Read Rate Performance

| Reader<br>Mode<br>ID* | Reader Mode<br>Optimization | Forward<br>Link<br>Modulation | Tari<br>(µs) | PIE | BLF<br>(kHz) | Back-<br>scatter<br>Link<br>Modulation | Typical<br>Optimized<br>Read Rate<br>(tags/s) |

|-----------------------|-----------------------------|-------------------------------|--------------|-----|--------------|----------------------------------------|-----------------------------------------------|

| 4323                  | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 2.0 | 640          | BPSK M=2                               | 700                                           |

| 4345                  | ETSI UB Hybrid              | PR-ASK                        | 7.5          | 1.5 | 640          | BPSK M=4                               | 450                                           |

| 4222                  | ETSI LB Hybrid              | PR-ASK                        | 20           | 2.0 | 320          | BPSK M=2                               | 300                                           |